JETIR.ORG

ISSN: 2349-5162 | ESTD Year: 2014 | Monthly Issue

# JOURNAL OF EMERGING TECHNOLOGIES AND INNOVATIVE RESEARCH (JETIR)

An International Scholarly Open Access, Peer-reviewed, Refereed Journal

# Analysis of a Modified Interleaved Non-Isolated Cuk Converter with reduced Ripple content

#### S. Naveenkumar

M.Tech, Department of Electrical Engineering

Andhra University College of Engineering(A)

Visakhapatnam, Andhra Pradesh, India.

### Dr. M. Gopi Chand Naik

Professor, Department of Electrical Engineering,

Andhra University College of Engineering(A)

Visakhapatnam, Andhra Pradesh, India.

# S. Rajendra Prasad

Research Scholar, Department of Electrical Engineering,

Andhra University College of Engineering(A)

Visakhapatnam, Andhra Pradesh, India.

#### **ABSTRACT**

DC – DC converters are one of the major components in most of the power electronic equipment's. In the future, renewable energy sources will be the primary energy sources due to non-renewable energy resources depletion. Having a sustainable energy source as an input voltage source for the electrical system is essential. These converters find applications in switched mode power supplies, battery operated electric vehicles, LED drivers for lighting, DC micro grids, battery chargers, DC welding solar power conditioners, and power conversion equipment's in DC transmissions, covering different ranges of power such as low, medium and high specifically for power conversion processes. The basic circuit topology for DC – DC converters offers the buck and boost facility, utilized for power handling. They provide pulsed currents either on input or on output side, due to the availability of inductor either at input or at output. The pulsed power affects the power quality, which is required is to be very high, to avoid injection of harmonics to the parent source.

This thesis Present here with an aim to analyse, simulate and examine the Operation of non-isolated Cuk and interleaved Cuk/Chook Converter. Here, Input Voltage of proposed Converter was maintaining below the 50 V to keep the cost of our operation low and moderate. Existing Traditional Cuk converter (TCC) has the Continuous Current at input as well as output side. This proclivity of Converter is taken for our performance Observation to analyse the behaviour of proposed Structure.

In Accordance with that, non-isolated interleaved Cuk/Chook Converter (ICC) is to be schemed/overtures and simulated here, to inspect the reduction in the ripple content on input and output waveform and it also enhances the Settling time of system. These unwanted ripple content is diminished or almost eliminated by implementing the Interleaved structure to existing converter topology with the current and voltage feedback control loop. Cuk Converter topology (TCC and ICC) gives output voltage with negative Polarity as compared to input voltage polarity. This interleaved configuration of converter is useful to achieve high gain and efficiency with

limited duty cycle and wide load variation range.

Keywords—DC-DC Converter Configuration, Interleaving Cuk Converter Technique, Reduced current and voltage ripple, Voltage Feedback.

#### I. INTRODUCTION

All SMPS topologies are imitated their behaviour in the particular set of boundaries. There are plenty number of Converters are anticipated, though minor alteration in basic DC-DC Converters are observed. The basic group of DC-DC Converters contains mainly three topologies: Buck, Boost and Buck-Boost Converter.in Buck Converter energy goes to the load when the switch is close. Whereas, in boost converter energy goes to load when the switch is open. Cuk Converter transfer the energy continuously. Moreover, Buck, Boost, Buck-Boost Converter have pulsed waveform either on input or output side. The Cuk Converter essentially a Boost-Buck converter. Little while ago, Interleaved Configuration has been widely introduced due to its some specific benefit, one of the main advantages is lower ripple content on output side and reduction in settling time. Higher current ripple may cut down lifespan of sources.so we have to expurgate the unwanted portion from the result. Here, in present paper, an interleaved Cuk Converter with wide conversion ratio is envisioned. The Contrived Configuration has feature like step up and step-down competence, lower ripple content, and a wide load variation range.

#### II. CUK CONFIGURATION

Major benefit behind usage of Non-Isolated Cuk-Converter is to supply the purely regulate DC output voltage over the buck-boost converter and other DC-DC topologies.it reduce the ripple content in input as well as output side with an improvement in settling time period. The CUK may be viewed as a Current-Voltage-Current Converter. Current source should be made in such a way so that it can delivers its whole energy into Voltage sink. This Voltage Source should be discharged into a Current Sink and Current Source should be discharged into a Voltage sink. The first case would eliminate current stress while the second one will eliminate the voltage stress. Exchange of energy takes place between the Source of potential energy and a sink of Kinetic energy and Vice-versa. Output voltage of Proposed Converter may be either high or low as compared to input Voltage, and it has negative voltage output. Input Sided Inductor would filter the ripple and provide smooth output. in order to hinder the large ripple, In Earlier Existing Converter Configuration Energy transferred through the inductor. For the Proposed Cuk converter, Energy transferred through the Capacitor.

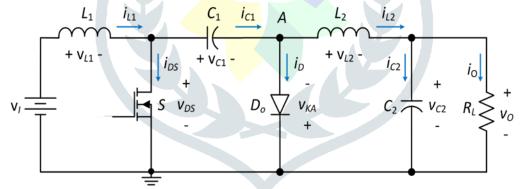

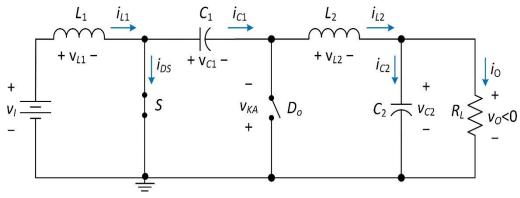

Figure 1: Traditional CUK Converter

#### III. WORKING PRINCIPLE OF CUK CONVERTER

Traditional Cuk Converter circuit consists of input inductor  $L_1$ , filter inductor  $L_1$ , energy storage capacitor  $C_1$ , filter capacitor  $C_2$ , input source  $V_1$ , load resistance  $R_L$ , MOSFET S and diode  $D_0$ . The input voltage  $V_1$  is applied produces the output voltage  $V_0$  measure across load resistance  $R_L$ . The input and output inductors ensure the delivery of continuous currents on both sides. The operation of the converter is based on capacitor energy transfer, the capacitor  $C_1$  acts as primary means of storing and transferring energy from the input to the output. The average inductor voltages  $V_{L1}$  and  $V_{L2}$  are zero at steady state. The capacitor  $C_1$  is designed in such a way that it transfers the constant voltage. The circuit has low switching losses and high efficiency. The converter operation is explained in two modes as given below.

#### • Time interval 0 < t < DT

Figure 2: Equivalent circuit of the non-isolated Cuk dc-dc converter, when the switch is on and the diode is off. During this time interval, the diode is in the off-state and the switch is in the on state. The equivalent circuit for this operation during the switch on cycle is shown in Fig. 2. The input inductor is connected parallel to the input voltage source.

The voltage across the inductor  $L_1$  is

$$v_{L1} = V_I = L_1 \frac{di_{L1}}{dt}$$

[1]

The peak-to-peak current of inductor L<sub>1</sub> is formulated as

$$\Delta i_{L1} = i_{L1}(DT) - i_{L1}(0) = \frac{DV_I}{f_S L_1}$$

[2]

The voltage across the capacitor  $C_1$  is

$$V_{C1} = V_{I} + V_{O}$$

[3]

The voltage across the inductor L2 is

$$v_{L2} = v_{C1} - V_O = L_2 \frac{di_{L1}}{dt}$$

[4]

The peak-to-peak current of inductor L2 is

$$\Delta i_{L2} = i_{L2}(DT) - i_{L2}(0) = \frac{DV_I}{f_S L_2}$$

[5]

# • Time interval $DT < t \le T$

Figure 3: Equivalent circuit of the Cuk dc-dc converter, when the switch is off and the diode is on.

During this time interval, the diode is on-state and the switch is off-state. The intermediate circuit indicating this operation during the switch OFF cycle is shown in Fig 3.

The voltage across the inductor L<sub>1</sub> is

$$v_{L1} = V_I - v_{C1} = L_1 \frac{di_{L1}}{dt}$$

[6]

The peak-to-peak current of inductor L<sub>1</sub> is formulated as

$$\Delta i_{L1} = i_{L1}(T) - i_{L1}(DT) = -\frac{(1-D)V_0}{f_S L_1}$$

[7]

By neglecting the inductor  $L_1$  ripple current, the voltage across the capacitor  $C_1$  is

$$v_{C1}(t) = \frac{1}{C_1} \int_0^t I_1 dt + v_{C1}(DT)$$

[8]

The ripple in capacitor voltage at t = T is

$$\Delta v_{C1} = v_{C1}(T) - v_{C1}(DT) = \frac{I_1(1-D)}{f_S C_1}$$

[9]

The voltage across the inductor L<sub>2</sub> is

$$v_{L2} = -V_0 = L_2 \frac{di_{L2}}{dt}$$

[10]

The peak-to-peak current of inductor L<sub>2</sub> is given by

$$\Delta i_{L2} = i_{L2}(DT) - i_{L2}(0) = -\frac{(1-D)V_0}{f_S L_2}$$

[11]

#### DC Voltage Gain

The volt-second balance principle states that the average voltage across the inductor at steady-state is equal to zero. By applying this principle to the inductor  $L_1$ , we get

$$\int_0^T v_L dt = 0$$

[12]

$$\int_{0}^{T} v_{L} dt = 0$$

$$\int_{0}^{DT} v_{L1}(t)dt + \int_{DT}^{T} v_{L1}(t)dt = 0$$

[12]

Using (2.12) (2.15), we obtain (2.27)

$$DV_1 - (1 - D)V_0 = 0 [14]$$

$DV_1 - (1-D)V_0 = 0 \label{eq:DV_DC}$  Hence, the dc input-to-output voltage gain  $M_{V\,DC}$  of the Cuk converter in CCM is

$$M_{V_{DC}} = \frac{V_0}{V_1} = -\frac{D}{1 - D} = -\frac{D}{D'}$$

[15]

# IV. DESIGN OF CUK CONVERTER

Design of a Cuk converter to operate in CCM with following specifications: Input voltage,  $V_I = 24V$ ; Output voltage,  $V_O = -48V$ ; Power output  $P_O = 40W$ ; Load resistance  $R_L = 48\Omega$ ; Switching frequency = 20kHz.

From Eqn. (2.8) the duty cycle is,

$$M_{V_{DC}} = \frac{V_0}{V_1} = -\frac{D}{1-D} = \frac{-48}{24} = -2$$

$$D = \frac{1}{3} = 0.66$$

Average inductor current

$$I_{L1} = \frac{P_I}{V_I} = \frac{50}{24} = 2.083A$$

$$I_{L2} = \frac{P_I}{-V_O} = \frac{50}{-(-48)} = 1.0417A$$

From Eqn. (2.4) input inductor  $L_1$  is,

$$\Delta i_{L1} = \frac{DV_I}{f_S L_1}$$

$$L_1 = \frac{DV_I}{f_S \Delta i_{L1}} = 0.19 \text{mH}$$

From Eqn. (2.24) input inductor  $L_2$  is,

$$\Delta i_{L2} = -\frac{(1-D)V_0}{f_S L_2}$$

$$L_2 = -\frac{(1-D)V_0}{f_S \Delta i_{L2}} = 3mH$$

Input Capacitor C1,

$$C_1 = \frac{DV_0}{Rf_s \Delta V_{C1}} = 0.6mF$$

Output Capacitor C2,

$$C_2 = \frac{(1 - D)V_{C2}}{(8L_2f_s^2)\Delta V_{C2}} = 22\mu F$$

By strictly following the above equation and putting our subsequent value of particular parameter, we obtain the optimal magnitude for the each and every specific component. Here, below table shows the obtained value for designing the particular element/component.

| Parameter                                    | Cuk Converter design parameters values |  |  |

|----------------------------------------------|----------------------------------------|--|--|

| Input Voltage (V <sub>I</sub> )              | 24V                                    |  |  |

| Output Voltage (Vo)                          | -48V                                   |  |  |

| Output Power (P <sub>O</sub> )               | 50W                                    |  |  |

| Switching Frequency (f <sub>s</sub> )        | 20kHz                                  |  |  |

| Duty Cycle (D)                               | 66%                                    |  |  |

| Capacitor (C <sub>1</sub> , C <sub>2</sub> ) | 0.15mH, 2mH                            |  |  |

| Inductor (L <sub>1</sub> , L <sub>2</sub> )  | 0.6mF, 22μF                            |  |  |

| Load Resistance                              | 48Ω                                    |  |  |

Table 1 : Cuk Converter design parameters

#### • Transfer function of Cuk Converter

After running the code in MATLAB, we get the transfer function G(S) is,

$$G(S) = \frac{1.246e^{07}S + 5.666e^{13}}{S^4 + 380.2S^3 + 5.58e^6S^2 - 1.392e^9S - 6.322e^{12}}$$

#### • Ziegler-Nichols Method

PID controller is faster and less oscillating than PI controller. But with small changes in the input set point, the PID controller tends to be more unstable than PI controller even in the case of distortion. The Ziegler-Nichols Method is one of the most effective methods to increase the use of PID controllers. First, it is checked whether the desired proportional control gain is positive or negative [22]. This critical Kp value is reached as "Critical Gain", Kc, and the period in which the oscillation occurs is called Pu "Critical Time Period". As a result, the whole process depends on two variables and other control parameters are calculated according to Table 4.1. Ziegler-Nichols method values used in the calculation for control parameters are shown in the table below. The transfer function of the system is calculated in the designed interface.

The critical gain of the transfer function generated by using the Ziegler-Nichols method was calculated as critical gain,  $K_u$  = 0.222, critical time period ( $T_u$ ) = 1.361msec. The required control parameter values (P, PI, PID) for system control were calculated with the critical gain and critical time period calculated before. The values of PID controller parameters were selected as Proportional gain ( $K_p$ ) = 0.1,  $K_s$ i = 87.975, Derivative gain ( $K_s$ d) = 0.000017

| Control Type | Кр                  | Ki                                  | K <sub>d</sub>    |

|--------------|---------------------|-------------------------------------|-------------------|

| P            | 0.5*K <sub>C</sub>  |                                     | -                 |

| PI           | 0.45*K <sub>u</sub> | 0.54*K <sub>u</sub> /T <sub>u</sub> | -                 |

| PID          | 0.6*K <sub>u</sub>  | 1.2*K <sub>u</sub> /T <sub>u</sub>  | $(0.6*K_u*T_u)/8$ |

Table 2: ZIEGLER-NICHOLS method Parameters

| Parameter                       | Values           |

|---------------------------------|------------------|

| Ku                              | 0.222            |

| Tu                              | 1.361msec        |

| K <sub>p</sub>                  | 0.1              |

| K <sub>i</sub> , K <sub>d</sub> | 87.975, 0.000017 |

**Table 3: PID Parameter design values**

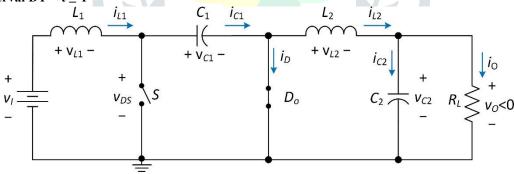

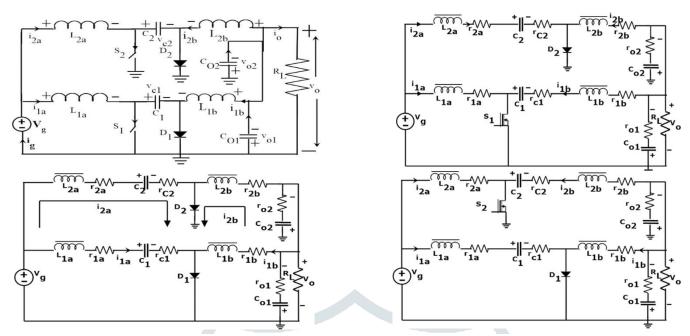

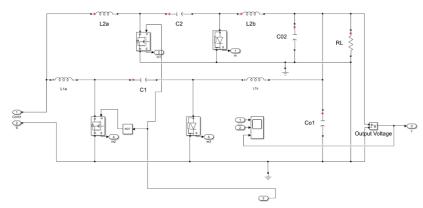

# V. INTERLEAVED CUK CONFIGURATION

Interleaved technique means connection in parallel. Here connecting two Cuk converters in parallel gives interleaved Cuk converter. This converter divides the high input current and improves current shape on input side and Temperature losses are reduced by using the two switches during the total time-period of operation i.e., during first half of the time-period (Ton/2) one switch $(S_1)$  is closed and another switch $(S_2)$  is opened. Similarly, during second half of the time-period (Ton/2) switch $(S_2)$  is closed and switch $(S_1)$  is opened. An ICC is developed with improved efficiency and superior and better transient performance and defeat the demerits of Cuk converter configuration. This technique provides continuous current on both sides and reduces switching current stress.

Circuit Diagram:

Figure 4: Operating Modes of ICC

Mode 1:  $S_1$  ON &  $S_2$  OFF: - The circuit diagram when switches  $S_1$  ON and  $S_2$  OFF as shown in the figure (b). During this period L1a andL2a discharges. The stored energy in  $L_{2a}$  transfers to  $C_2$  and it charges. Also, the capacitor  $C_1$  discharges through  $C_1$ ,  $S_1$ ,  $C_{O1}$ ,  $L_{1b}$ ,  $C_{O2}$ ,  $L_{2b}$  and  $R_L$ , hence transfers stored energy in the capacitors to the load. The load current is assumed constant and flows in negative direction.

Mode 2 -S<sub>1</sub> OFF & S<sub>2</sub> OFF: -The circuit diagram when both switches S<sub>1</sub> and S<sub>2</sub> are in OFF condition is shown in figure (b). During this period inductors L<sub>1a</sub> and L<sub>2a</sub> are discharging and stored energy transfers to capacitors C<sub>1</sub> & C<sub>2</sub> respectively. Also, C<sub>1</sub> starts charging. At the same time inductors L<sub>1b</sub>& L<sub>2b</sub> are discharging as shown in figure (d)transfers its energy to load.

Mode 3-  $S_1$  OFF &  $S_2$  ON: -The equivalent circuit when the switches  $S_1$  OFF and  $S_2$  ON is shown in the figure (d). During this period  $L_{2a}$  charges and  $L_{1a}$  discharges. The stored energy in  $L_{1a}$  transfers to  $C_1$  and it continuous to charge. Also, the capacitor  $C_2$  discharges through  $C_2$ ,  $C_2$ ,  $C_2$ ,  $C_2$ ,  $C_2$ ,  $C_3$ ,  $C_4$  and  $C_4$ . Hence transfers stored energy in the capacitor to the load.

| Compo.<br>Name | Stage-1(S1 ON) | Stage-2(OFF) | Stage-3(S2 ON) |

|----------------|----------------|--------------|----------------|

|                |                |              |                |

| $L_{1a}$       | Charging       | Dis-Charging | Dis-Charging   |

| $L_{1b}$       | Charging       | Dis-Charging | Dis-Charging   |

| $L_{2a}$       | Dis-Charging   | Dis-Charging | Charging       |

| $L_{2b}$       | Dis-Charging   | Dis-Charging | Charging       |

| $C_1$          | Dis-Charging   | Charging     | Charging       |

| $C_2$          | Charging       | Charging     | Dis-Charging   |

| Co             | Dis-Charging   | Charging     | Charging       |

**Table 4: Operation Mode of ICC**

# **VI. SIMULATION RESULTS**

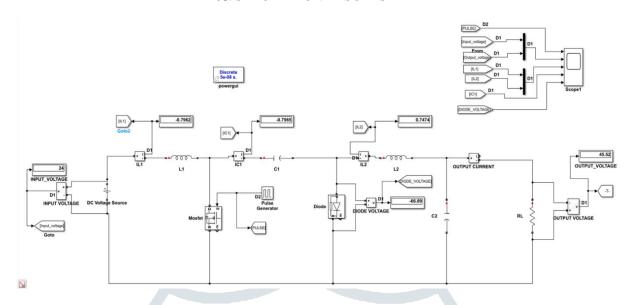

Figure 5: Cuk Converter Simulink Model

# • Simulation Results of Cuk Converter

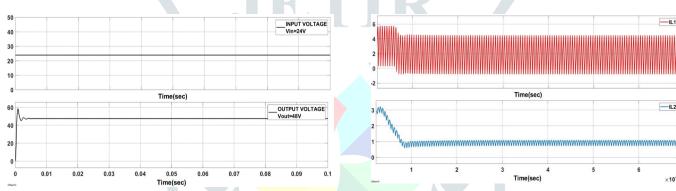

Figure 6 : Input - Output Voltage Waveform

Figure 7: Input - Output Current Waveform

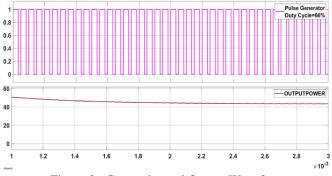

Figure 8: Gate pulse and Output Waveform

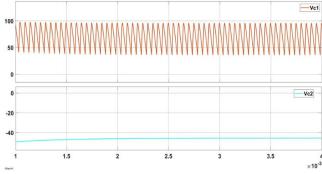

Figure 10: Voltage across Capacitors

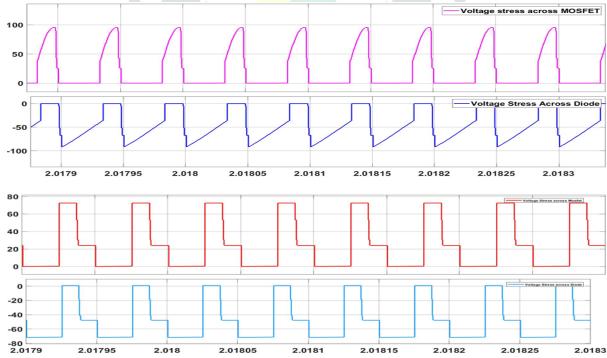

Figure 9 : Voltage stress across Switches

Figure 11: Output Voltage and Current Waveforms

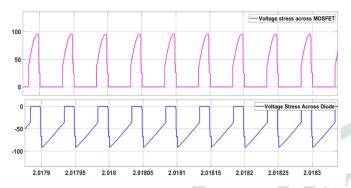

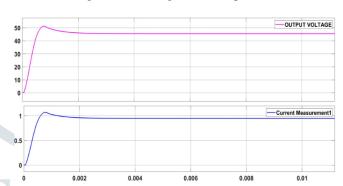

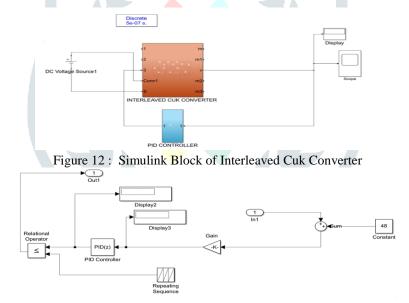

# • Simulation Results of Interleaved Cuk Converter

Figure 13: PID Controller of Interleaved Cuk converter

Figure 14: Simulation Diagram of Interleaved Cuk Converter

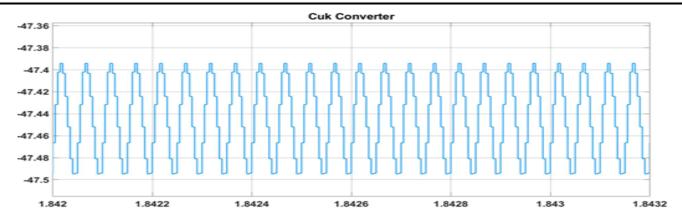

Figure 15: Output Voltage Comparison between Cuk and Interleaved Cuk Converter

The Output Voltage ripple comparison is shown in the above Fig.7.11

Output Ripple of Conventional Cuk Converter is 0.10 V

Output Ripple of Interleaved Cuk Converter is 0.01 V.

So, we are getting almost negligible ripple from Interleaved Cuk Converter.

$$\frac{0.10 - 0.01}{0.10} = 90\%$$

Almost 90% ripple is reduced by using Interleaved Cuk Converter

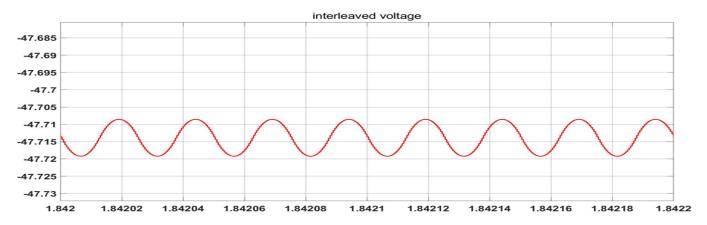

Figure 16: Device stresses comparison

Device Stresses in Cuk Converter is 100V.

Device stresses in Interleaved Cuk Converter is 70V.

% Of Reduction =

$$\frac{100-70}{100}$$

= 30%.

We are getting 30% voltage stress reduction by using Interleaved Cuk Converter instead of Conventional Cuk Converter

#### VII. CONCLUSION

The first selection of the thesis introduces the idea of how to reduce the input current ripple and output voltage ripple of DC-DC converter. This topic is limited to isolated DC-DC converters especially Conventional Cuk Converter and Interleaved Cuk Converter. Cuk Converter output ripple is somewhat high because of this drawback the usage of Cuk Converter is limited in MPPT Tracking and wind generation. Another observation in this converter is the device stresses are very high.

In this thesis, closed loop control for traditional Cuk converter and proposed interleaved Cuk converter is to be performed using MATLAB 2021b Software. Value of converter component are calculated by applying steady state analysis and controller design is done through the dynamic modelling. Transfer function is obtained by state space analysis of each converter. By using transfer function, the PID controller is designed through Ziegler Nicholas method. By analysing the different variable Waveform one can conclude that ripple is reduced from 0.10volts to 0.01 volts (almost 90% of the ripple is reduced). Switch Stress is decreased due to implementation of interleaved structure.

#### VIII. REFERENCES

- [1] Ned Mohan, Tore M Undeland, William P Robbins, Power Electronics: Converters, Applications and Design, Singapore, Media Enhanced 3rd ed.; John Wiley & sons Inc., 2003

- [2] N. K. Poon, J. C. P. Liu, C. K. Tse and M. H. Pong, "Techniques for Input Ripple Current Cancellation: Classification and Implementation," IEEE Trans. Power Electron., Vol. 15, no. 6, pp.1144-1152, Nov. 2000.

- [3] Joseph K.D., Daniel A.E., Unnikrishnan A.: 'Reduced ripple interleaved Cuk converter with phase shifted PWM'. IEEExplore, Kota, Kinabalu, Malaysia, May 2015, pp. 1–6

- [4] B. Singh, B. N. Singh, A. Chandra, K. Al-Haddad, A. Pandey, and D. P. Kothari, "A review of single-phase improved power quality ac–dc converters," IEEE Trans. Ind. Electron., vol. 50, no. 5, pp. 962–981, Oct. 2003.

- [5] DC to DC Converters Cuk and Sepic Converter, Versión 2 EE IIT, Kharagpur(NPTEL)

- [6] Ramshaw, R.S. (1993) Power Electronic Semiconductor Switches. 2nd ed. London: Chapman & Hall

- [7] S. M. Ćuk, "Modelling, Analysis, and Design of Switching Converters," Ph.D. dissertation, California Institute of Technology, Pasadena, Nov.1976.

- [8] Kamil, M. (13/11/07) Switched Mode Power Supply (SMPS) Topologies (Part I). Available at: http://ww1.microchip.com/downloads/en/AppNotes/01114A.pdf

- [9] Switching Power Supply Design,3<sup>rd</sup> Edition, Abraham I. Pressman, Keith Billings, Taylor Morey,Mc Graw Hill Publication

- [10] S Karenina, Timothy L. (2002) The Power Electronics Handbook Industrial Electronics Series. USA: CRC Press LLC

- [11] Sanjeev singh and Bhim singh,"Voltage Controlled PFC Cuk Converter-Based PMBLDCM Drive for AirCinditioner,"in Proc.IEEE TRANS. ON INDUSTRY APPLICATION, VOL. 48, NO. 2, Apr 2012.pp832-838

- [12] Boopathy K and Dr. Boopathy Bagan K,"Buck Boost Converter with improved transient response for low power application"in Proc. IEEE SIEA,Sep 2011,pp. 155-160